Wat is 'advanced packaging'?

In de halfgeleiderindustrie verwijst ‘packaging’ naar de laatste fase van het chipproductieproces, waarin de chip fysiek wordt ingekapseld en gekoppeld aan zijn omgeving. Traditioneel gebeurde dat met draadverbindingen of flip-chips. Maar inmiddels is er een revolutie gaande in de vorm van advanced packaging: technieken die meerdere chips (zoals processors en geheugenelementen) combineren tot één compact, krachtig en energie-efficiënt geheel.

Denk aan het samenbrengen van verschillende functionele eenheden in één verpakking, net zoals foodproducenten een maaltijdpakket samenstellen met verschillende componenten — maar dan op microniveau. Niet ter bescherming alléén, maar ook om prestaties, snelheid en samenwerking tussen onderdelen te optimaliseren. De verpakking wordt dus onderdeel van de werking zelf.

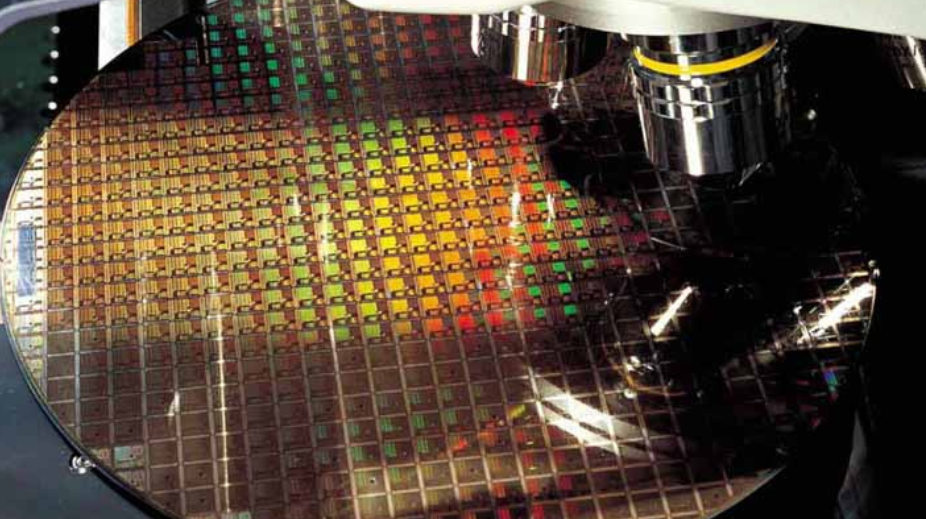

Beeld: Taiwan Semiconductor Manufacturing Co., Ltd.

Klein maar krachtig

Volgens McKinsey verschuift de innovatie in de chipwereld steeds meer van het begin van het productieproces (het ontwerpen en fabriceren van de chip) naar de achterkant: de verpakking. Moore’s Law — het idee dat het aantal transistors op een chip elke twee jaar verdubbelt — raakt zijn grenzen. Om toch te blijven innoveren, kijken chipmakers nu naar hoe ze bestaande componenten slimmer kunnen verpakken en verbinden.

Technieken zoals CoWoS (Chip-on-Wafer-on-Substrate), fan-out wafer-level packaging en 3D-stacking maken het mogelijk om meerdere chips op elkaar of naast elkaar te plaatsen in één module. Zo ontstaat een systeem dat sneller, krachtiger én compacter is — met toepassingen in AI, datacenters, mobiele telefoons, automotive en meer.

Chips-on-wafer (CoW) is een geavanceerde verpakkingsaanpak waarbij meerdere afzonderlijke chips worden gemonteerd op een gemeenschappelijke wafer voordat verdere stappen zoals encapsulatie of verbinding met een ondergrond plaatsvinden. Dit is een belangrijk onderdeel van sommige moderne packagingtechnologieën zoals CoWoS (Chip-on-Wafer-on-Substrate), ontwikkeld door het Taiwanese bedrijf TSMC.

Bij fan-out wafer-level packaging (FOWLP) wordt de chip na fabricage eerst losgesneden (gediced) van de wafer. Daarna wordt hij uitgebreid (fan-out) door hem in te kapselen in een kunststofmateriaal, waarbij rondom extra ruimte ontstaat. In die ruimte worden vervolgens redistributielagen (RDL) aangebracht — geleidende sporen die verbindingen leggen naar de buitenwereld.

Anders kijken

Voor professionals in de conventionele verpakkingssector biedt deze ontwikkeling een kans om anders naar het verpakken te kijken. Ook bij consumentenverpakkingen zien we een verschuiving van louter fysieke bescherming naar integrale systeemoplossingen. Denk aan slimme verpakkingen die realtime data geven over temperatuur of versheid, verpakkingen die direct communiceren met productieketens, of modulaire verpakkingssystemen voor e-commerce en foodservice.

Advanced chip packaging laat zien dat verpakking óók een motor van innovatie kan zijn — een strategische factor, geen sluitpost. De chipindustrie illustreert dat de verpakking niet alleen moet beschermen en bij elkaar houden, maar ook verbinden, versnellen en sturen.

Copyright:Taiwan Semiconductor Manufacturing Co., Ltd.

Lessen uit de chipwereld

Welke inspiratie kunne verpakkingsprofessionals uit de ontwikkeling halen? Verpakken als middel om ruimte te besparen en als element van ketenintegratie.

Formaat is functie. Net zoals fan-out-technologie een platte, compacte configuratie mogelijk maakt, zien we ook bij consumentenverpakkingen dat ruimtebesparing, opslagoptimalisatie en distributie-efficiëntie steeds belangrijker worden. En wat de ketenintegratie betreft: In de chipsector werken ontwerpers, fabless bedrijven en verpakkingsspecialisten nauw samen vanaf het eerste ontwerpstadium. Ook in verpakkingen is co-creatie tussen producent, designer en verpakkingspartner cruciaal is voor innovatie en ook steeds gewoner geworden.

De verpakking als strategisch instrument

De les van McKinsey is helder: wie verpakkingen blijft zien als logistiek sluitstuk, mist kansen. De koplopers in de chipindustrie maken van de verpakking een concurrentievoordeel — een middel om klanten te binden, prestaties te verhogen en technologie tastbaar te maken.

Voor de verpakkingsindustrie biedt dit stof tot nadenken én inspiratie. Verpakken hoeft niet altijd om dozen, kratten of trays te gaan. Soms begint de echte innovatie op het kleinste schaalniveau denkbaar.

Bron: McKinsey & Company, Advanced chip packaging: How manufacturers can play to win (mei 2023).

beeld: copyright

Taiwan Semiconductor Manufacturing Co., Ltd.